本文如果有错,欢迎留言更正;此外,转载请标明出处 ,作者:IC_learner

这里来讲一下formality的使用,貌似跟tcl和DC没有很强的联系;然而说没有联系,也是不正确的。在综合完成之后,可以进行形式验证。此外这里不是专门讲解formality的使用的,因此只会简单地实践一下它的用法。

formality是Synopsys公司的形式验证工具,上一节我们得到了综合后的设计,这里我们就要验证综合后的设计和我们的RTL代码是否一致。

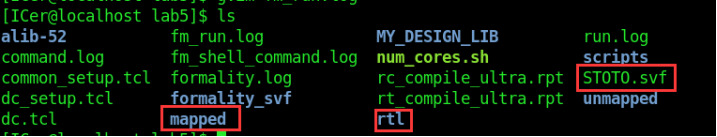

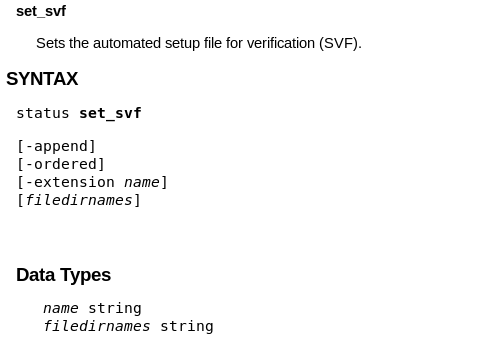

1、准备好RTL文件、综合优化后的文件以及带有优化映射信息的SVF文件:

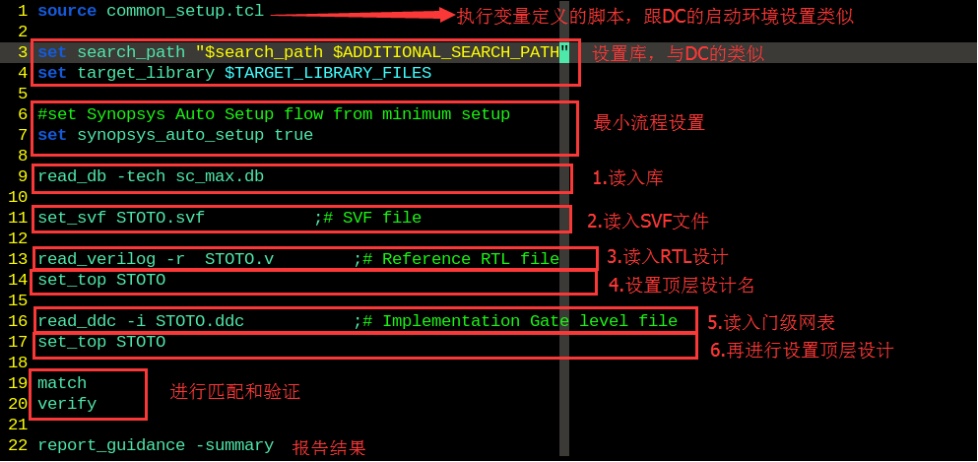

2、书写相应地流程文件:

3、启动formality:

fm_shell

对上面脚本不清楚的或者不懂的,可以使用man命令查看它的用法:

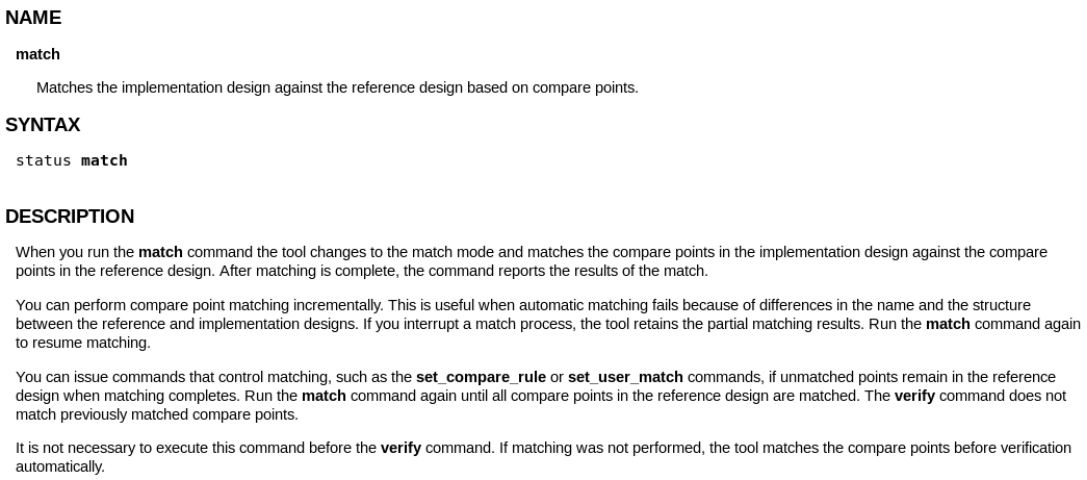

-->

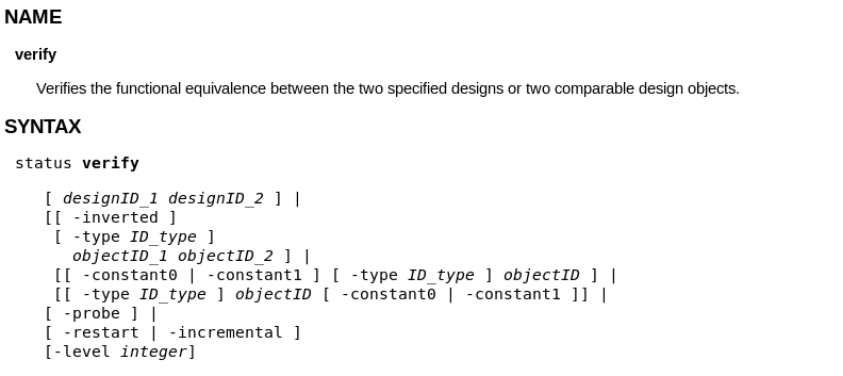

-->

-->

-->

4、执行我们写的脚本

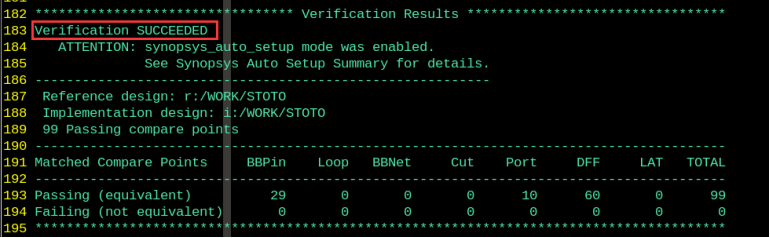

得到结果如下,说明验证通过了: